# *Q*-Enhancement of Spiral Inductor with $N^+$ -Diffusion Patterned Ground Shields

Y. Emery Chen, David Bien\*, Deukhyoun Heo, and Joy Laskar

Microelectronics Research Center, School of Electrical and Computer Engineering

Georgia Institute of Technology, 791 Atlantic Drive, Atlanta, GA 30332, USA

\* Motorola SPS, Tempe, AZ 85284, USA

**Abstract** — This paper discusses the quality factor enhancement by employing different patterned ground shields underneath the simple spiral inductor in a commercial BiCMOS technology. The effectiveness of the patterned ground shield technique depends heavily on the counter-effects between the reduction of substrate loss and the increase of parasitic capacitance. With proper choice of the shielding layer, the quality factor can achieve 21% enhancement for a 5-nH spiral inductor. The  $n^+$ -diffusion layer is found to be the most effective layer for the patterned ground shield technique due to less associated parasitic capacitance.

## I. INTRODUCTION

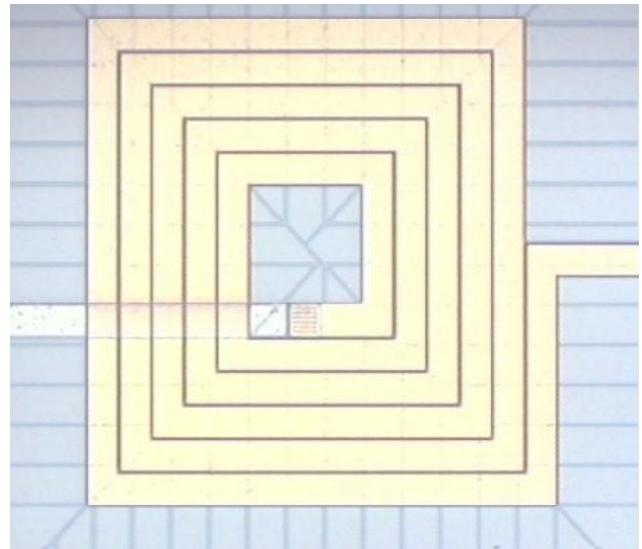

With continuous improvement of device performance, CMOS and BiCMOS technologies have become viable alternatives for RFIC designs [1], [2]. However, manufacturing on-chip inductors of high quality factor ( $Q$ ) in a commercial CMOS/BiCMOS technology is still a challenge. One of the major technical difficulties to implement high- $Q$  inductors on Si is the lossy substrate. The patterned ground shield technique is proposed to reduce the loss of the inductor through Si substrate [3]. A conductive plane is employed underneath an inductor to shield the electromagnetic field from the substrate. In order to mitigate the effect of the induced eddy current on the conductive shielding plane, the plane is cut with the slots perpendicular to the traces of the inductor as shown in Fig. 1.

The *polysilicon* layer is reported to be the most effective layer in the CMOS technology as the pattern ground shields [3], but this implementation in terms of  $Q$ -enhancement is not robust. Several papers reported that the *polysilicon* patterned ground shield actually degrades the  $Q$ s of the spiral inductors [4], [5]. The effects of induced parasitic capacitance due to the insertion of the *polysilicon* patterned ground shield are often overlooked. In this paper, we explore the effective implementation of the pattern ground shield technique by inserting different

shielding layers underneath the simple spiral inductors. The  $n^+$ -diffusion patterned ground shielding is found to be the most effective implementation for  $Q$ -enhancement. An inductor model is presented to explain the experimental result and the effectiveness of the different patterned ground shields.

Fig. 1. A simple spiral inductor with a patterned ground shield underneath.

## II. INDUCTOR DESIGN

Several kinds of patterned ground shield inductors are implemented in a commercial low-cost RF BiCMOS technology. The equivalent inductance of all the inductors is about 5 nH at 1 GHz. The trace width and spacing of the inductors are fixed to be 15  $\mu\text{m}$  and 2  $\mu\text{m}$ , respectively. The center hollow area of the inductors is 60 x 60  $\mu\text{m}^2$ . The different shielding layers underneath

the simple spiral include *polysilicon* patterned ground shield (PPG), *metal-1* patterned ground shield (MPG), and  $n^+$ -*diffusion* patterned ground shield (NPG).

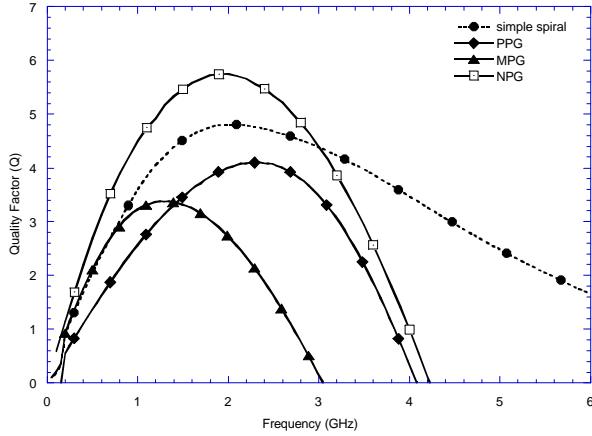

Fig. 2.  $Q$ s of the simple spiral inductor and the inductors with different patterned ground shields including: *polysilicon* patterned ground shield (PPG), *metal-1* patterned ground shield (MPG), and  $n^+$ -*diffusion* patterned ground shield (NPG).

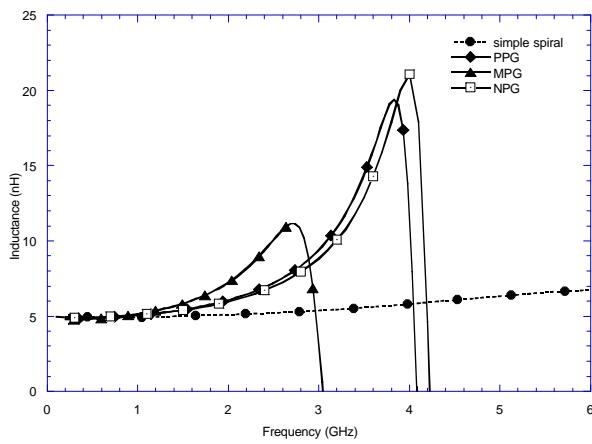

Fig. 3. Inductance of the simple spiral inductor and the patterned ground shield inductors.

### III. RESULTS AND DISCUSSIONS

The  $Q$ s of the inductors are extracted by the one-port characterization [4] as Eq. (1).

$$Z = \frac{1 + \Gamma}{1 - \Gamma} \times 50 \quad \text{and} \quad Q = \frac{\text{Im}(Z)}{\text{Re}(Z)} \quad (1)$$

where  $\Gamma$  is the reflection coefficient measured from the

on-port inductors. The  $Q$ s of the simple spiral inductors with different patterned ground shields are shown in Fig. 2. Compared with the inductor without patterned ground shield, both the *polysilicon* patterned ground shield (PPG) and *metal-1* patterned ground shield (MPG) can't improve the  $Q$ s of the inductors. The quality factor degradation of the MPG inductor is more severe than the PPG inductor. However, the  $n^+$ -*diffusion* patterned ground shield (NPG) inductor does show noticeable  $Q$  enhancement, up to 21%. The result is quite different from the previous report that the *polysilicon* is the most effective patterned ground shield layer to improve the  $Q$  of the inductor [3]. Based upon the previous papers [3]-[5] and experimental results, we can infer that the effectiveness of patterned ground shields for  $Q$  enhancement is very technology-dependent. The inductance of the simple spiral inductor and the different patterned ground shield inductors is shown in Fig. 3. The patterned ground shields don't change the inductance much below 1 GHz. Although the  $n^+$ -*diffusion* patterned ground shield inductor has much higher  $Q$  than the *polysilicon* patterned ground shield inductor, the self-resonant frequency of the former is just a little higher than the latter.

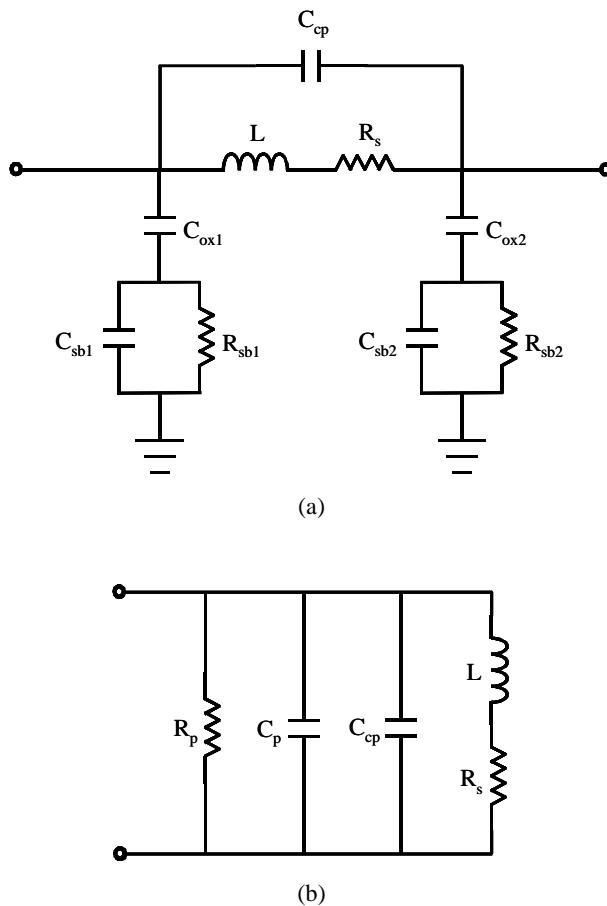

The model of the spiral inductor is shown in Fig. 4(a). The port-2 of the inductor is connected to ground to derive the input impedance ( $Z$ ) looking into the port-1. To further simplify the derivation, the oxide capacitance,  $C_{ox1}$ , and the substrate parasitics,  $C_{sb1}$  and  $R_{sb1}$ , can be replaced by the equivalent circuit of the resistor  $R_p$  and the capacitor  $C_p$  in parallel, as shown in Fig. 4(b), where

$$R_p = \frac{1}{w^2 C_{ox1}^2 R_{sb1}} + \frac{R_{sb1} (C_{ox1} + C_{sb1})^2}{C_{ox1}^2} \quad (2)$$

$$C_p = C_{ox1} \cdot \frac{1 + w^2 (C_{ox1} + C_{sb1}) C_{sb1} R_{sb1}^2}{1 + w^2 (C_{ox1} + C_{sb1})^2 R_{sb1}^2} \quad (3)$$

The  $Q$  of the inductor can be derived as

$$\begin{aligned} Q &= \frac{\text{Im}(Z)}{\text{Re}(Z)} \\ &= \frac{wL}{R_s} \cdot \frac{R_p}{R_p + \left[ \left( \frac{wL}{R_s} \right)^2 + 1 \right] R_s} \\ &\quad \left[ 1 - \frac{R_s^2 (C_{cp} + C_p)}{L} - w^2 L (C_{cp} + C_p) \right] \\ &= \frac{wL}{R_s} \cdot \text{resistor loss factor} \cdot \text{capacitor loss factor} \end{aligned} \quad (4) \quad (5)$$

Table 1

Models of the inductors with patterned ground shields

| Inductor Models | $L$ (nH) | $R_s$ ( $\Omega$ ) | $C_{cp}$ (fF) | $C_{ox1}$ (pF) | $R_{sb1}$ ( $\Omega$ ) | $C_{sb1}$ (fF) |

|-----------------|----------|--------------------|---------------|----------------|------------------------|----------------|

| Simple inductor | 4.80     | 6.32               | 37.3          | 0.361          | 622                    | 26.7           |

| PPG inductor    | 4.66     | 6.40               | 37.9          | 0.629          | 483                    | 490            |

| MPG inductor    | 4.36     | 6.01               | 35.5          | 4.124          | 418                    | 669            |

| NPG inductor    | 4.81     | 6.10               | 37.1          | 0.377          | 520                    | 32.5           |

where the resistor loss factor and capacitor loss factor are always smaller than 1, and the  $Q$  can be enhanced if the loss factors approach unity. Eq. (2) and (4) suggest that the resistor loss factor will approach unity if  $R_{sb1}$  becomes either infinitely large or infinitely small. A high resistance substrate can improve the  $Q$  of the inductor because of high  $R_{sb1}$  while pattern ground shields improve the  $Q$  by providing a low resistance ground path; that is, low  $R_{sb1}$ .

Fig. 4. (a) Typical spiral inductor model. (b) Simplified one-port inductor model.

However, deploying a ground shield underneath the inductor also introduces additional parasitic capacitance, which will distribute to  $C_{ox1}$  and  $C_{sb1}$ . The closer the ground shields to the inductors, the larger the additional parasitic capacitance. From Eq. (2) ~ (4), the additional capacitance could deteriorate both the resistor and capacitor loss factors severely. The lumped-element components in the models of the patterned ground shield inductors are shown in Table 1. All of the patterned ground shields reduce the  $R_{sb1}$  of the inductors. The *polysilicon* and *metal-1* patterned ground shields increase the  $C_{ox1}$  and  $C_{sb1}$  tremendously, but the  $n^+$ -*diffusion* patterned ground shield doesn't increase the  $C_{ox1}$  and  $C_{sb1}$  much due to the larger distance between the spiral inductor layer and the shielding layer. This explains why the *metal-1* and *polysilicon* patterned ground shields degrade the  $Q$ s of the inductors while  $n^+$ -*diffusion* patterned ground shield shows the  $Q$  improvement.

#### IV. CONCLUSIONS

The patterned ground shield technique for the  $Q$ -enhancement of spiral inductors is vulnerable to the induced parasitic capacitance of the ground shields. The  $n^+$ -*diffusion* patterned ground shield is more effective than the *polysilicon* patterned ground shield for  $Q$ -enhancement because of less associated parasitic capacitance. In our experiment, the  $n^+$ -*diffusion* patterned ground shields can improve the  $Q$  up to 21% for a 5-nH spiral inductor.

#### ACKNOWLEDGEMENT

The authors wish to acknowledge for the assistance and support of National Semiconductor Corporation and Yamacraw Research Center. They would like to thank especially Thomas R. Anderson, who is previously with National Semiconductor and currently with Gain Technology, for invaluable discussions.

## REFERENCES

- [1] S. P. Voinigescu, S. W. Tarasewicz, T. MacElwee, and J. Ilowski, "An assessment of the state-of-the-art 0.5  $\mu$ m bulk CMOS technology for RF application," *Proceedings, IEEE International Electron Devices Meeting*, pp. 721-724, Dec. 1995.

- [2] Rainer Gotzfried, Frank Beisswanger, and Stephan Gerlach, "Design of RF integrated circuits using SiGe bipolar technology," *IEEE Journal of Solid-State Circuits*, vol. 33, no. 9, pp. 1417-1422, Sept. 1998.

- [3] C. Patrick Yue, S. Simon Wong, "On-Chip Spiral Inductors with Patterned Ground Shields for Si-Based RF IC's," *IEEE Journal of Solid-State Circuits*, vol. 33, no. 5, pp. 743-751, May 1998.

- [4] Y. J. E. Chen, D. Heo, J. Laskar, and T. Anderson, "Investigation of Q Enhancement for Inductors Processed in BiCMOS Technology," *Proceedings, IEEE Radio and Wireless Conference*, pp. 263-266, Aug. 1999.

- [5] C. M. Hung and K. O. Kenneth, "A 1.24 GHz Monolithic CMOS VCO with Phase Noise of -137 dBc/Hz at a 3-MHz Offset," *IEEE Microwave and Guided Wave Letters*, vol. 9, no. 3, pp. 111-113, March 1999.